ข้อมูลจำเพาะ

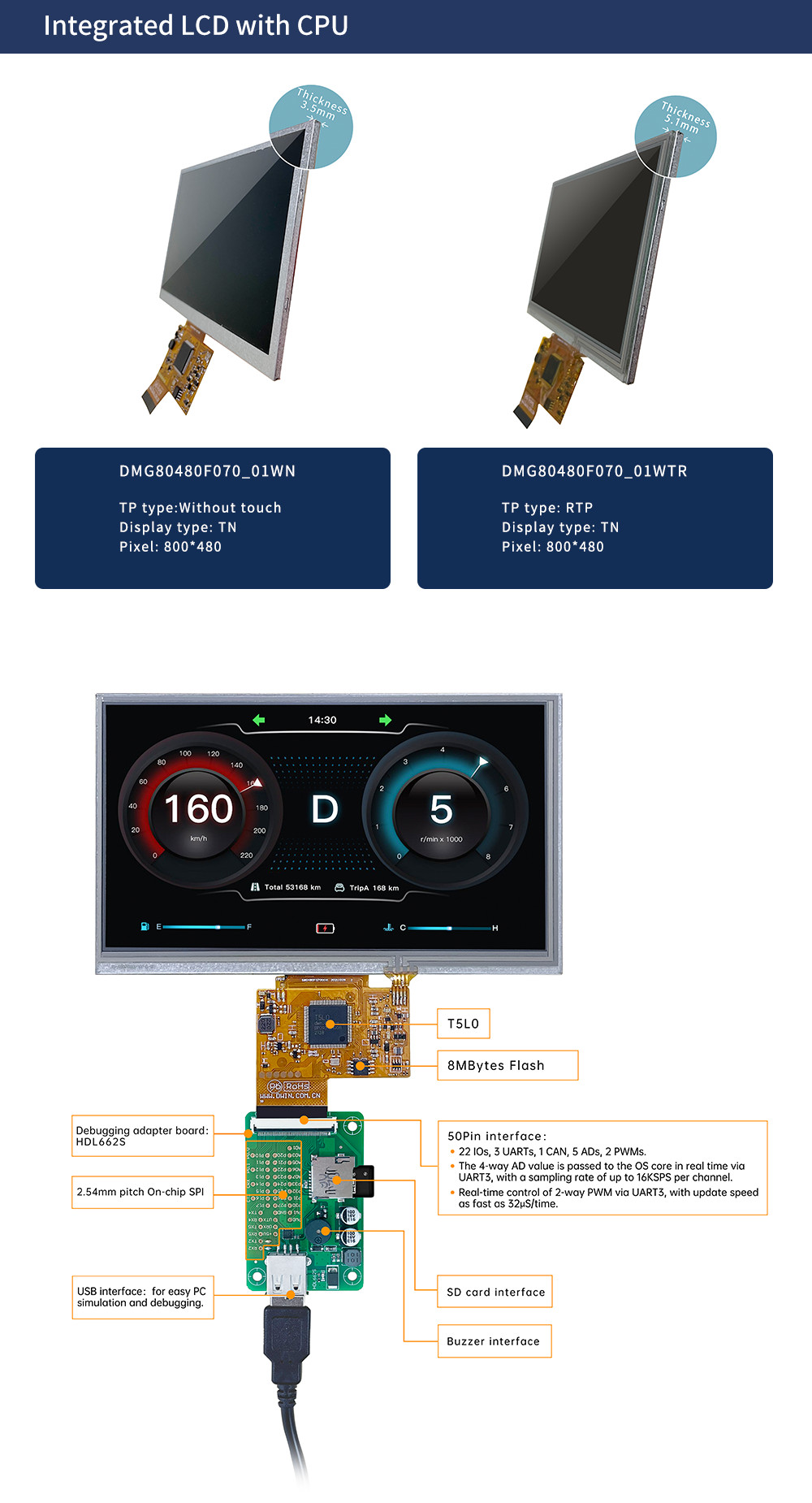

| T5L0 ASIC | พัฒนาโดย DWIN การผลิตจำนวนมากในปี 2020,1MBytes หรือ Flash บนชิป, พื้นที่จัดเก็บข้อมูลแปรผัน 128Kbytes สำหรับการแลกเปลี่ยนข้อมูลกับ OS CPU Core และหน่วยความจำ รอบการเขียนซ้ำ: มากกว่า 100,000 ครั้ง | ||

| สี | 262,000 สี | ||

| ประเภทจอแอลซีดี | เทนเนสซี, TFT LCD | ||

| มุมมอง | มุมมองปกติ ค่าทั่วไป 70°/70°/30°/40°(L/R/U/D) | ||

| พื้นที่แสดงผล (AA) | 154.08 มม. (กว้าง) × 85.92 มม. (สูง) | ||

| ปณิธาน | 800×480 | ||

| แสงไฟ | นำ | ||

| ความสว่าง | DMG80480F070_01WN: 250nit | ||

| DMG80480F070_01WTR: 200nit | |||

| พิมพ์ | RTP (แผงสัมผัสแบบต้านทาน) | ||

| โครงสร้าง | ฟิล์มนี้+แก้วนี้ | ||

| โหมดสัมผัส | รองรับการสัมผัสและลากจุด | ||

| ความแข็งพื้นผิว | 3ชม | ||

| การส่งผ่านแสง | มากกว่า 80% | ||

| ชีวิต |

แต้ม > 1,000,000 ครั้ง; โรคหลอดเลือดสมอง > 100,000 ครั้ง; แรง 150 กรัม, ด้านหลัง และออกไปนับเป็นสองเท่า | ||

| แรงดันไฟฟ้า | 3.6~5.5V | ||

| การดำเนินงานปัจจุบัน | VCC = +5V, เปิดแบ็คไลท์, 410mA | ||

| VCC = +5V, ปิดแบ็คไลท์, 115mA | |||

| อุณหภูมิในการทำงาน | -10°C~60°C | ||

| อุณหภูมิในการจัดเก็บ | -20°C~70°C | ||

| ความชื้นในการทำงาน | 10% ~ 90% RH ค่าทั่วไป 60% RH | ||

| บอดเรต | 3150~3225600bps | ||

| แรงดันขาออก | เอาต์พุต 1, Iout = 8mA; 3.0~3.3V | ||

| เอาท์พุต 0, ออก =-8mA; 0~0.3V | |||

| แรงดันไฟฟ้าขาเข้า(รับ) | อินพุต 1; 3.3V | ||

| อินพุต 0; 0 ~ 0.5V | |||

| อินเตอร์เฟซ | UART2: TTL; | ||

| UART4: TTL; ( ใช้ได้เฉพาะหลังจากการกำหนดค่า OS เท่านั้น) | |||

| UART5: TTL; (ใช้ได้เฉพาะหลังจากการกำหนดค่า OS เท่านั้น | |||

| รูปแบบข้อมูล | UART2: N81; | ||

| UART4: N81/E81/O81/N82; 4 โหมด (การกำหนดค่าระบบปฏิบัติการ) | |||

| UART5: N81/E81/O81/N82; 4 โหมด (การกำหนดค่าระบบปฏิบัติการ) | |||

| เบ้า | 50พิน_0.5มม. เอฟพีซี | ||

| แฟลช | 8M ไบต์ | ||

| เข็มหมุด | คำนิยาม | ฉัน/โอ | รายละเอียดการทำงาน |

| 1 | +5V | ฉัน | แหล่งจ่ายไฟ DC3.6-5.5V |

| 2 | +5V | ฉัน | |

| 3 | จีเอ็นดี | จีเอ็นดี | จีเอ็นดี |

| 4 | จีเอ็นดี | จีเอ็นดี | |

| 5 | จีเอ็นดี | จีเอ็นดี | |

| 6 | AD7 | ฉัน |

ADC อินพุต 5 ตัว ความละเอียด 12 บิต ในกรณีของแหล่งจ่ายไฟ 3.3V อินพุต 0-3.3V แรงดันไฟฟ้า. ยกเว้น AD6 ข้อมูลที่เหลือจะถูกส่งไปยัง OS core ผ่าน UART3 ใน เรียลไทม์ด้วยอัตราการสุ่มตัวอย่าง 16KHz สามารถใช้ AD1 และ AD5 ได้ ขนานและ AD3 และ AD7 สามารถใช้แบบขนานได้ซึ่งเท่ากับสอง โฆษณาสุ่มตัวอย่าง 32KHz AD1,AD3,AD5,AD7 สามารถใช้งานแบบขนานได้ซึ่ง เท่ากับโฆษณาสุ่มตัวอย่าง 64KHz; ข้อมูลจะถูกรวมเข้าด้วยกัน 1,024 ครั้งและ จากนั้นหารด้วย 64 เพื่อให้ได้ค่า AD 64Hz 16 บิตโดยการสุ่มตัวอย่างมากเกินไป |

| 7 | AD6 | ฉัน | |

| 8 | AD5 | ฉัน | |

| 9 | AD3 | ฉัน | |

| 10 | AD1 | ฉัน | |

| 11 | +3.3 | โอ | เอาต์พุต 3.3V โหลดสูงสุด 150mA |

| 12 | เอสพีเค | โอ |

MOSFET ภายนอกเพื่อขับเคลื่อนเสียงกริ่งหรือลำโพง ตัวต้านทานภายนอก 10K ควรดึงลงไปที่พื้นเพื่อให้แน่ใจว่าการเปิดเครื่องอยู่ในระดับต่ำ |

| 13 | SD_ซีดี | ไอโอ |

อินเทอร์เฟซ SD/SDHC, SD_CK เชื่อมต่อตัวเก็บประจุ 22pF กับ GND ใกล้ อินเทอร์เฟซการ์ด SD |

| 14 | SD_CK | โอ | |

| 15 | SD_D3 | ไอโอ | |

| 16 | SD_D2 | ไอโอ | |

| 17 | SD_D1 | ไอโอ | |

| 18 | SD_D0 | ไอโอ | |

| 19 | PWM0 | โอ |

2 เอาต์พุต PWM 16 บิต ควรดึงตัวต้านทาน 10K ภายนอกลงไป กราวด์เพื่อให้แน่ใจว่าการเปิดเครื่องอยู่ในระดับต่ำ แกนระบบปฏิบัติการสามารถควบคุมได้แบบเรียลไทม์ผ่าน UART3 |

| 20 | PWM1 | โอ | |

| ยี่สิบเอ็ด | หน้า 3.3 | ไอโอ |

หากใช้ RX8130 หรือ SD2058 I2C RTC เพื่อเชื่อมต่อกับ IO ทั้งสอง SCL ควรเชื่อมต่อกับ P3.2 และ SDA เชื่อมต่อกับ P3.3 แบบขนาน พร้อมตัวต้านทาน 10K ดึงได้ถึง 3.3V |

| ยี่สิบสอง | หน้า 3.2 | ไอโอ | |

| ยี่สิบสาม | P3.1/EX1 | ไอโอ |

สามารถใช้เป็นอินพุตอินเทอร์รัปต์ภายนอก 1 ได้ในเวลาเดียวกันและ รองรับทั้งโหมดแรงดันไฟฟ้าต่ำหรือโหมดขัดจังหวะขอบท้าย |

| ยี่สิบสี่ | P3.0/EX0 | ไอโอ |

สามารถใช้เป็นอินพุตขัดจังหวะภายนอก 0 ในเวลาเดียวกันและ รองรับทั้งโหมดแรงดันไฟฟ้าต่ำหรือโหมดขัดจังหวะขอบท้าย |

| 25 | หน้า 2.7 | ไอโอ | อินเทอร์เฟซไอโอ |

| 26 | หน้า 2.6 | ไอโอ | อินเทอร์เฟซไอโอ |

| 27 | หน้า 2.5 | ไอโอ | อินเทอร์เฟซไอโอ |

| 28 | หน้า 2.4 | ไอโอ | อินเทอร์เฟซไอโอ |

| 29 | หน้า 2.3 | ไอโอ | อินเทอร์เฟซไอโอ |

| 30 | หน้า 2.2 | ไอโอ | อินเทอร์เฟซไอโอ |

| 31 | หน้า 2.1 | ไอโอ | อินเทอร์เฟซไอโอ |

| 32 | P2.0 | ไอโอ | อินเทอร์เฟซไอโอ |

| 33 | หน้า 1.7 | ไอโอ | อินเทอร์เฟซไอโอ |

| 34 | หน้า 1.6 | ไอโอ | อินเทอร์เฟซไอโอ |

| 35 | หน้า 1.5 | ไอโอ | อินเทอร์เฟซไอโอ |

| 36 | หน้า 1.4 | ไอโอ | อินเทอร์เฟซไอโอ |

| 37 | หน้า 1.3 | ไอโอ | อินเทอร์เฟซไอโอ |

| 38 | หน้า 1.2 | ไอโอ | อินเทอร์เฟซไอโอ |

| 39 | หน้า 1.1 | ไอโอ | อินเทอร์เฟซไอโอ |

| 40 | P1.0 | ไอโอ | อินเทอร์เฟซไอโอ |

| 41 | UART4_TXD | โอ | UART4 |

| 42 | UART4_RXD | ฉัน | |

| 43 | UART5_TXD | โอ | UART5 |

| 44 | UART5_RXD | ฉัน | |

| 45 | P0.0 | ไอโอ | อินเทอร์เฟซไอโอ |

| 46 | หน้า 0.1 | ไอโอ | อินเทอร์เฟซไอโอ |

| 47 | CAN_TX | โอ | สามารถเชื่อมต่อได้ |

| 48 | CAN_RX | ฉัน | |

| 49 | UART2_TXD | โอ | UART2 (พอร์ตอนุกรม UART2 ของแกน OS) |

| 50 | UART2_RXD | ฉัน |