Especificação

| T5L0 ASIC | T5L0 ASIC é um ASIC de baixo consumo de energia, econômico, GUI e aplicativo altamente integrado de chip único e dual-core, projetado pela DWIN Technology para LCD de tamanho pequeno e produzido em massa em 2020. | ||

| Cor | 16,7 milhões de cores | ||

| Tipo LCD | IPS, LCD TFT | ||

| Ângulo de visão | Ângulo de visão normal, valor típico de 70°/70°/50°/70°(L/R/U/D) | ||

| Área de exibição (AA) | 108,00 mm (L) × 64,80 mm (A) | ||

| Resolução | 800*480 | ||

| Luz de fundo | LIDERADO | ||

| Brilho | 300 nits | ||

| Tensão de energia | 3,6~5,5V | ||

| Corrente de Operação | 520mA VCC = 5V, luz de fundo máxima | ||

| 150mA VCC = 5V, luz de fundo desligada | |||

| Temperatura de trabalho | -10℃~60℃ | ||

| Temperatura de armazenamento | -20℃~70℃ | ||

| Umidade de trabalho | 10% ~ 90% UR, valor típico de 60% UR | ||

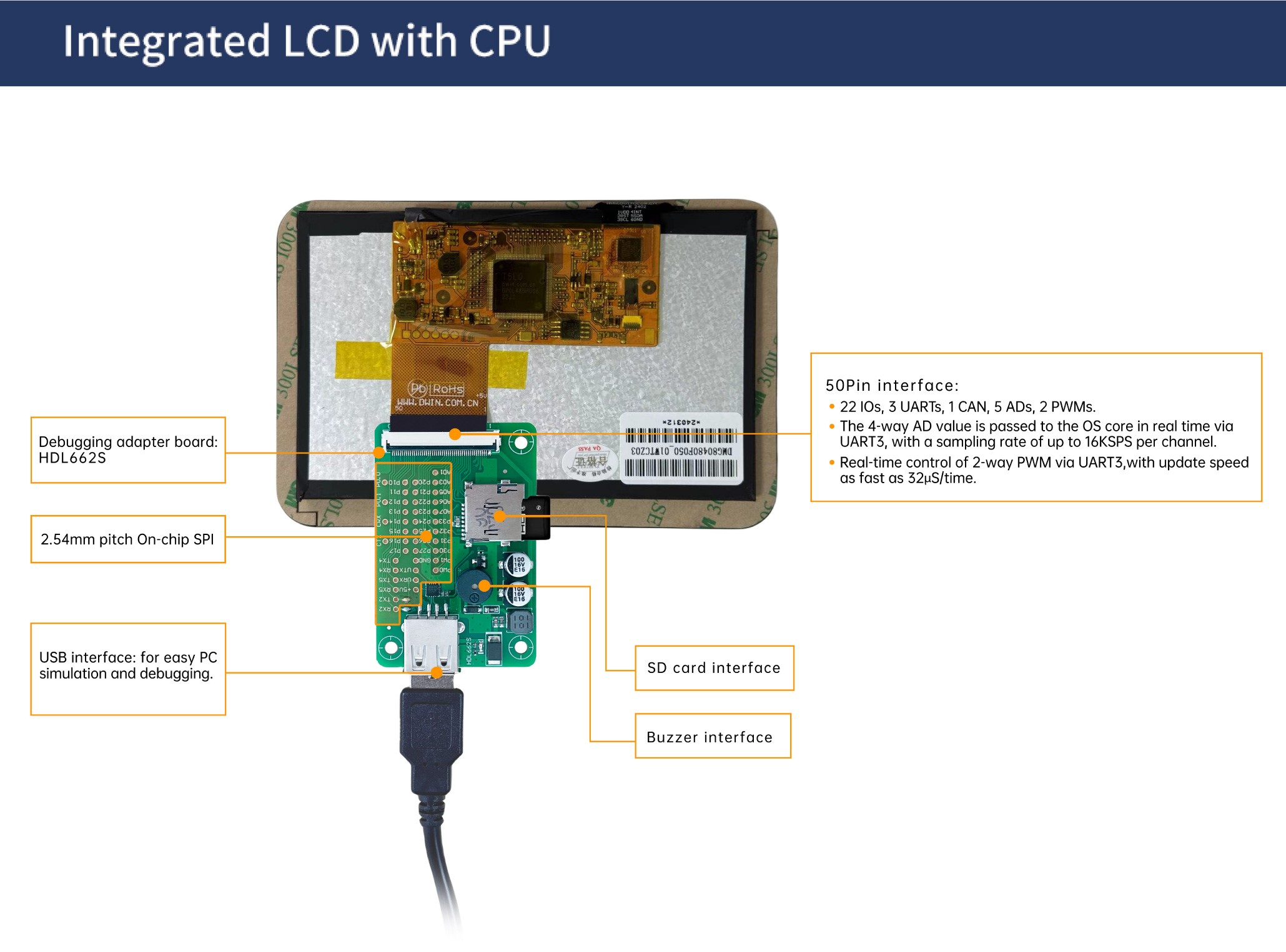

| Interface de usuário | 50 pinos_0,5 mm FPC | ||

| Taxa de transmissão | 3150~3225600bps | ||

| Voltagem de saída | Saída 1;3,0~3,3 V | ||

| Saída 0;0~0,3 V | |||

|

Tensão de entrada | Entrada 1;3.3V | ||

| Entrada 0;0~0,5V | |||

| Interface |

UART2: TTL; UART4: TTL;(Disponível somente após a configuração do sistema operacional UART5: TTL;(Disponível somente após configuração do sistema operacional) | ||

| Formato de dados |

UART2: N81; UART4: N81/E81/O81/N82;4 modos (configuração do sistema operacional) UART5: N81/E81/O81/N82;4 modos (configuração do sistema operacional) | ||

| Alfinete | Definição | E/S | Descrição Funcional |

| 1 | 5V | EU | Fonte de alimentação, DC3.6-5.5V |

| 2 | 5V | EU | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | EU | 5 ADCs de entrada. Resolução de 12 bits no caso de fonte de alimentação de 3,3V. Tensão de entrada de 0-3,3 V. Exceto para AD6, os demais dados são enviados ao núcleo do sistema operacional via UART3 em tempo real com taxa de amostragem de 16KHz. AD1 e AD5 podem ser usados em paralelo, e AD3 e AD7 podem ser usados em paralelo, o que equivale a dois AD de amostragem de 32KHz. AD1, AD3, AD5, AD7 podem ser usados em paralelo, o que equivale a uma amostragem AD de 64KHz; os dados são somados 1.024 vezes e depois divididos por 64 para obter um valor AD de 64 Hz e 16 bits por sobreamostragem. |

| 7 | AD6 | EU | |

| 8 | AD5 | EU | |

| 9 | AD3 | EU | |

| 10 | AD2 | EU | |

| 11 | 3.3 | O | Saída de 3,3V, carga máxima de 150mA. |

| 12 | SPK | O | MOSFET externo para acionar campainha ou alto-falante. O resistor externo de 10K deve ser puxado até o solo para garantir que a inicialização esteja em nível baixo. |

| 13 | SD_CD | E/S | Interface SD/SDHC, o SD_CK conecta um capacitor de 22pF ao GND próximo à interface do cartão SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | E/S | |

| 16 | SD_D2 | E/S | |

| 17 | SD_D1 | E/S | |

| 18 | SD_D0 | E/S | |

| 19 | PWM0 | O |

2 saídas PWM de 16 bits. O resistor externo de 10K deve ser puxado até o solo para garantir que a inicialização esteja em nível baixo. O núcleo do sistema operacional pode ser controlado em tempo real via UART3 |

| 20 | PWM1 | O | |

| vinte e um | P3.3 | E/S | Se estiver usando RX8130 ou SD2058 I2C RTC para conectar a ambos os IOs, o SCL deve ser conectado a P3.2 e o SDA conectado a P3.3 em paralelo com pull-up de resistor de 10K para 3,3V. |

| vinte e dois | P3.2 | E/S | |

| vinte e três | P3.1/EX1 | E/S | Ele pode ser usado como uma entrada externa de interrupção 1 ao mesmo tempo e suporta modos de interrupção de nível de baixa tensão ou de borda final. |

| vinte e quatro | P3.0/EX0 | E/S | Ele pode ser usado como uma entrada de interrupção 0 externa ao mesmo tempo e suporta modos de interrupção de nível de baixa tensão ou borda de fuga |

| 25 | P2.7 | E/S | Interface de E/S |

| 26 | P2.6 | E/S | Interface de E/S |

| 27 | P2.5 | E/S | Interface de E/S |

| 28 | P2.4 | E/S | Interface de E/S |

| 29 | P2.3 | E/S | Interface de E/S |

| 30 | P2.2 | E/S | Interface de E/S |

| 31 | P2.1 | E/S | Interface de E/S |

| 32 | P2.0 | E/S | Interface de E/S |

| 33 | P1.7 | E/S | Interface de E/S |

| 34 | P1.6 | E/S | Interface de E/S |

| 35 | P1.5 | E/S | Interface de E/S |

| 36 | P1.4 | E/S | Interface de E/S |

| 37 | P1.3 | E/S | Interface de E/S |

| 38 | P1.2 | E/S | Interface de E/S |

| 39 | P1.1 | E/S | Interface de E/S |

| 40 | P1.0 | E/S | Interface de E/S |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | EU | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | EU | |

| 45 | P0.0 | E/S | Interface de E/S |

| 46 | P0.1 | E/S | Interface de E/S |

| 47 | CAN_TX | O | Interface CAN |

| 48 | CAN_RX | EU | |

| 49 | UART2_TXD | O | UART2 (porta serial UART0 do núcleo do sistema operacional) |

| 50 | UART2_RXD | EU |