Specyfikacja

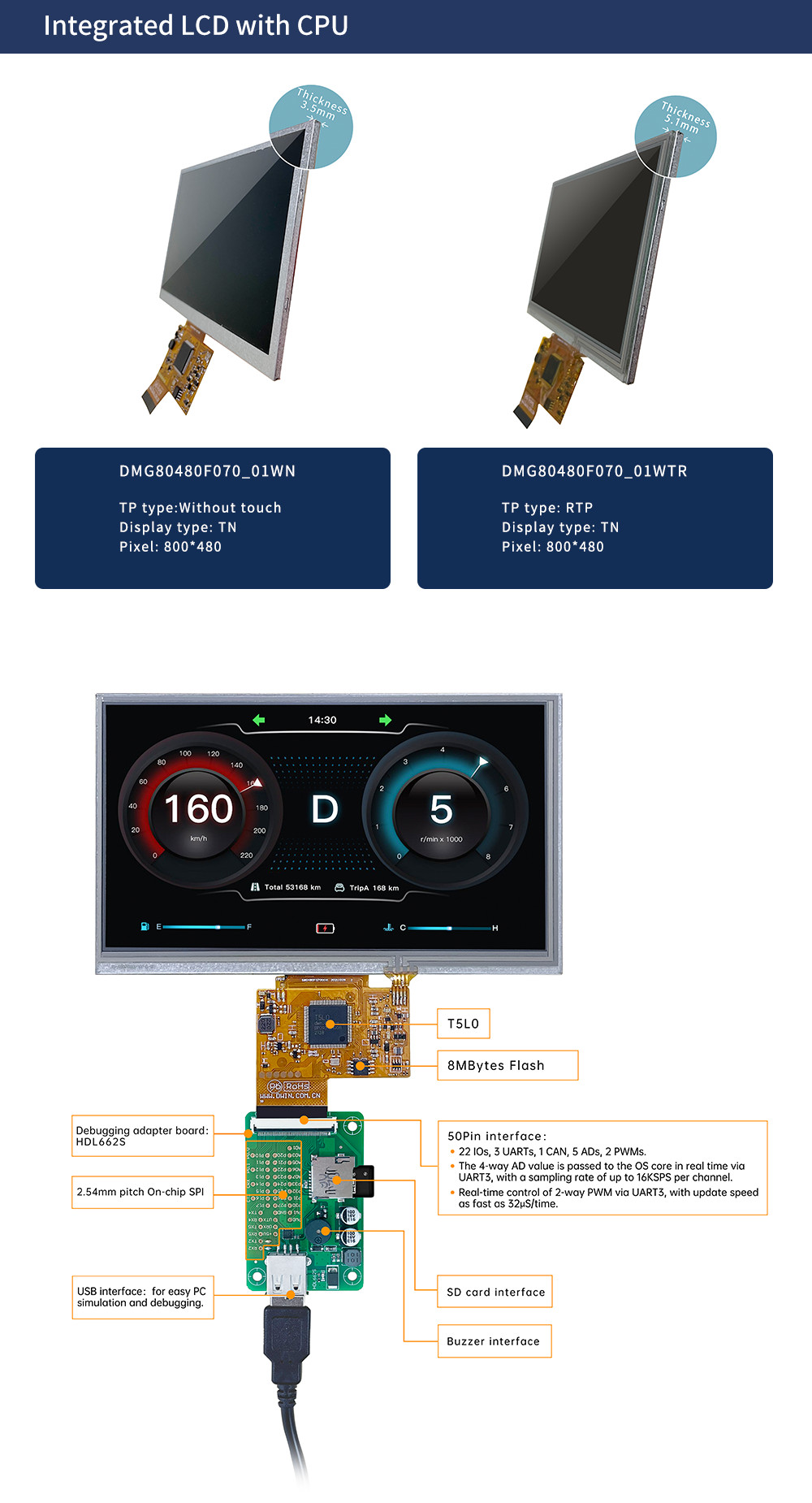

| Układ ASIC T5L0 | Opracowany przez DWIN. Produkcja masowa w 2020 r., 1 MB pamięci Nor Flash na chipie, 128 KB zmiennej przestrzeni dyskowej do wymiany danych z rdzeniem procesora i pamięcią systemu operacyjnego. Cykl przepisywania: ponad 100 000 razy | ||

| Kolor | 262 tys. kolorów | ||

| Typ LCD | TN, TFT LCD | ||

| Kąt widzenia | Normalny kąt widzenia, typowa wartość 70°/70°/30°/40° (L/R/U/D) | ||

| Obszar wyświetlania (AA) | 154,08 mm (szer.) × 85,92 mm (wys.) | ||

| Rezolucja | 800×480 | ||

| Podświetlenie | PROWADZONY | ||

| Jasność | DMG80480F070_01WN: 250 nitów | ||

| DMG80480F070_01WTR: 200 nitów | |||

| Typ | RTP (rezystancyjny panel dotykowy) | ||

| Struktura | TEN film + TO szkło | ||

| Tryb dotykowy | Punkt wsparcia dotknij i przeciągnij | ||

| Twardość powierzchni | 3H | ||

| Przepuszczalność światła | Ponad 80% | ||

| Życie |

Kropkowanie > 1 000 000 razy; Udar > 100 000 razy; Siła 150 g, tył i dalej, liczone jako dwa razy | ||

| Napięcie | 3,6 ~ 5,5 V | ||

| Prąd operacyjny | VCC = +5 V, podświetlenie włączone, 410 mA | ||

| VCC = +5 V, podświetlenie wyłączone, 115 mA | |||

| Temperatura pracy | -10 ℃ ~ 60 ℃ | ||

| Temperatura przechowywania | -20 ℃ ~ 70 ℃ | ||

| Wilgotność robocza | 10% ~ 90% RH, typowa wartość 60% RH | ||

| Szybkość transmisji | 3150~3225600bps | ||

| Napięcie wyjściowe | Wyjście 1, Iwy = 8 mA; 3,0 ~ 3,3 V | ||

| Wyjście 0, Iwy =-8mA; 0 ~ 0,3 V | |||

| Napięcie wejściowe(RXD) | Wejście 1;3,3 V | ||

| Wejście 0;0~0,5V | |||

| Interfejs | UART2: TTL; | ||

| UART4: TTL; (dostępne tylko po konfiguracji systemu operacyjnego) | |||

| UART5: TTL; (dostępne tylko po konfiguracji systemu operacyjnego). | |||

| Format danych | UART2: N81; | ||

| UART4: N81/E81/O81/N82; 4 tryby (konfiguracja systemu operacyjnego) | |||

| UART5: N81/E81/O81/N82; 4 tryby (konfiguracja systemu operacyjnego) | |||

| Gniazdo elektryczne | 50Pin_0,5mm FPC | ||

| Błysk | 8M bajtów | ||

| SZPILKA | Definicja | We/Wy | Opis działania |

| 1 | +5 V | I | Zasilanie, DC3,6-5,5V |

| 2 | +5 V | I | |

| 3 | GND | GND | GND |

| 4 | GND | GND | |

| 5 | GND | GND | |

| 6 | AD7 | I |

5 wejściowych przetworników ADC. Rozdzielczość 12-bitowa w przypadku zasilania 3,3V. Wejście 0-3,3 V Napięcie. Z wyjątkiem AD6, pozostałe dane są przesyłane do rdzenia systemu operacyjnego poprzez wejście UART3 w czasie rzeczywistym z częstotliwością próbkowania 16 kHz. Można stosować AD1 i AD5 równolegle, a AD3 i AD7 można używać równolegle, co równa się dwa Próbkowanie 32 kHz AD. AD1, AD3, AD5, AD7 mogą być używane równolegle, co równa się próbkowaniu AD o częstotliwości 64 kHz; dane sumuje się 1024 razy i następnie podzielono przez 64, aby uzyskać wartość AD 64 Hz, 16 bitów poprzez nadpróbkowanie. |

| 7 | AD6 | I | |

| 8 | AD5 | I | |

| 9 | AD3 | I | |

| 10 | AD1 | I | |

| 11 | +3,3 | O | Wyjście 3,3 V, maksymalne obciążenie 150 mA. |

| 12 | SPK | O |

Zewnętrzny MOSFET do sterowania brzęczykiem lub głośnikiem. Zewnętrzny rezystor 10K należy pociągnąć do podłoża, aby upewnić się, że poziom zasilania jest niski. |

| 13 | SD_CD | IO |

Interfejs SD/SDHC, SD_CK łączy kondensator 22pF z blisko GND interfejs karty SD. |

| 14 | SD_CK | O | |

| 15 | SD_D3 | IO | |

| 16 | SD_D2 | IO | |

| 17 | SD_D1 | IO | |

| 18 | SD_D0 | IO | |

| 19 | PWM0 | O |

2 16-bitowe wyjście PWM. Zewnętrzny rezystor 10K należy obniżyć do uziemienie, aby upewnić się, że poziom zasilania jest niski. Rdzeniem systemu operacyjnego można sterować w czasie rzeczywistym za pośrednictwem UART3 |

| 20 | PWM1 | O | |

| dwadzieścia jeden | P3.3 | IO |

Jeśli używasz RX8130 lub SD2058 I2C RTC do podłączenia obu wejść/wyjść, SCL powinien być podłączony do P3.2, a SDA podłączony równolegle do P3.3 z podciągnięciem rezystora 10 K do 3,3 V. |

| dwadzieścia dwa | P3.2 | IO | |

| dwadzieścia trzy | P3.1/EX1 | IO |

Może być jednocześnie używane jako wejście zewnętrznego przerwania 1 i obsługuje zarówno tryby przerwania niskiego napięcia, jak i zbocza spływu. |

| dwadzieścia cztery | P3.0/EX0 | IO |

Może być jednocześnie używane jako wejście zewnętrznego przerwania 0 i obsługuje zarówno tryby przerwania niskiego napięcia, jak i zbocza spływu. |

| 25 | P2.7 | IO | Interfejs I/O |

| 26 | P2.6 | IO | Interfejs I/O |

| 27 | P2.5 | IO | Interfejs I/O |

| 28 | P2.4 | IO | Interfejs I/O |

| 29 | P2.3 | IO | Interfejs I/O |

| 30 | P2.2 | IO | Interfejs I/O |

| 31 | P2.1 | IO | Interfejs I/O |

| 32 | P2.0 | IO | Interfejs I/O |

| 33 | P1.7 | IO | Interfejs I/O |

| 34 | P1.6 | IO | Interfejs I/O |

| 35 | P1.5 | IO | Interfejs I/O |

| 36 | P1.4 | IO | Interfejs I/O |

| 37 | P1.3 | IO | Interfejs I/O |

| 38 | P1.2 | IO | Interfejs I/O |

| 39 | P1.1 | IO | Interfejs I/O |

| 40 | P1.0 | IO | Interfejs I/O |

| 41 | UART4_TXD | O | UART4 |

| 42 | UART4_RXD | I | |

| 43 | UART5_TXD | O | UART5 |

| 44 | UART5_RXD | I | |

| 45 | P0.0 | IO | Interfejs I/O |

| 46 | P0.1 | IO | Interfejs I/O |

| 47 | CAN_TX | O | Interfejs CAN |

| 48 | CAN_RX | I | |

| 49 | UART2_TXD | O | UART2 (port szeregowy UART2 rdzenia systemu operacyjnego) |

| 50 | UART2_RXD | I |