Manyleb

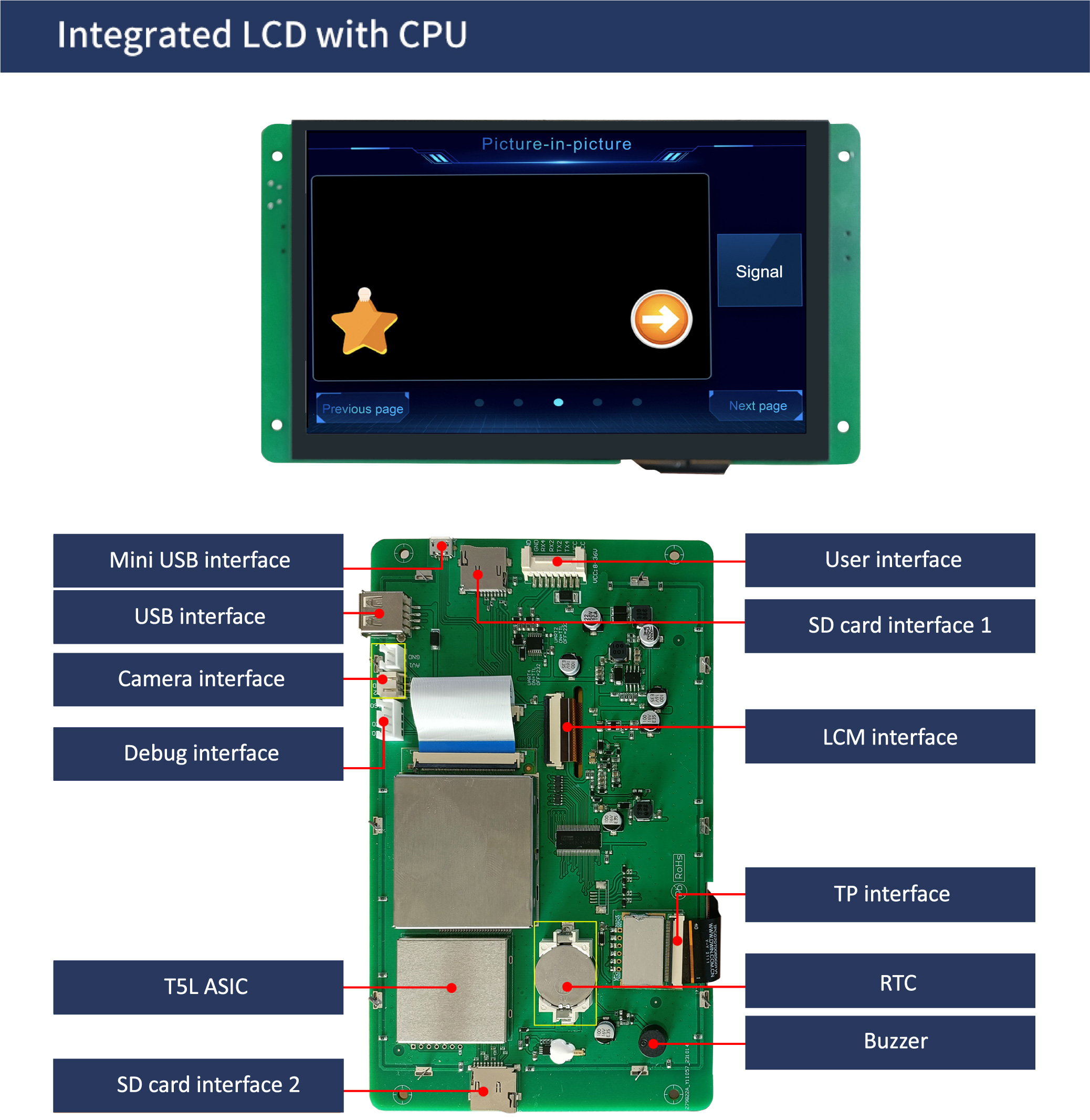

| T5L2 ASIC | Datblygwyd gan DWIN. Cynhyrchu màs yn 2019,1MBytes Na Flash ar y sglodion, 512KBytes a ddefnyddir i storio'r gronfa ddata defnyddwyr. Ailysgrifennu cylch: drosodd100,000 o weithiau |

| Rhyngwyneb LCM | FPC50_0.5mm, rhyngwyneb RGB |

| Rhyngwyneb TP | Cyffyrddiad capacitive: strwythur COB, rhyngwyneb IIC |

| Cyffyrddiad gwrthiannol: rhyngwyneb 4Pin_1.0mm | |

| Rhyngwyneb defnyddiwr | Soced 8Pin_2.0mm ar gyfer cyflenwad pŵer a chyfathrebu cyfresol. Cyfradd lawrlwytho (gwerth nodweddiadol): 12KByte yr eiliad |

| Fflach | 16 MBytes NOR Flash, ar gyfer ffontiau, lluniau a ffeiliau sain. Ailysgrifennu cylch: dros 100,000 o weithiau |

| Swniwr | 3V swnyn goddefol. Pwer: |

| RTC | Cell botwm ar gyfer cyflenwad pŵer, Cywirdeb: ± 20ppm @ 25 ℃ |

| Rhyngwyneb cerdyn SD 1 | Rhyngwyneb cerdyn SD R11, yn cefnogi arbed data delwedd sgrin |

| Rhyngwyneb cerdyn SD 2 | FAT32, gellir arddangos ffeiliau lawrlwytho trwy ryngwyneb SD mewn ystadegau, cyfradd lawrlwytho: 4Mb/s |

| Rhyngwyneb USB bach | Ar gyfer llosgi firmware R11 |

| Rhyngwyneb USB | Rhyngwyneb USB llorweddol, Wedi'i ddefnyddio ar gyfer llosgi firmware R11 |

| Rhyngwyneb siaradwr | Swyddogaeth ddim ar agor eto (NC) |

| Rhyngwyneb dadfygio | Rhyngwyneb 4Pin_ 2.54mm, RX0, TX0, rhyngwyneb dadfygio SPIO |

| Rhyngwyneb camera | Llorweddol 2pin_ 2.0mm * 1 a fertigol 2Pin_ 2.54mm * 1 (mewnbwn analog 1080P AHD HD, dwy derfynell, yn cefnogi mewnbynnau 1/2, yn cefnogi arddangosiad newid pan fydd wedi'i gysylltu â dwy sianel, ac nid yw'n cefnogi dwy sianel o'r un sgrin arddangos) |

| Math LCD | IPS, TFT LCD |

| Gweld Ongl | Ongl wylio eang, 85 ° / 85 ° / 85 ° / 85 ° (L / R / U / D) |

| Datrysiad | 1280 × 800 picsel (cefnogi 0 ° / 90 ° / 180 ° / 270 °) |

| Lliw | 24-did 8R8G8B |

| Ardal Actif (AA) | 149.8mm (W) × 93.6mm (H) |

| Modd Backlight | LED |

| Bywyd Gwasanaeth Backlight | > 20000 awr (Amser y disgleirdeb yn pydru i 50% ar gyflwr gweithio'n barhaus gyda'r disgleirdeb mwyaf) |

| Disgleirdeb | DMG12800T070_27WTC: 250nit |

| DMG12800T070_27WTR: 250nit | |

| Rheoli Disgleirdeb | Gradd 0 ~ 100 (Pan fydd y disgleirdeb yn cael ei addasu i 1% ~ 30% o'r disgleirdeb mwyaf, gall fflachio ddigwydd ac ni argymhellir ei ddefnyddio yn yr ystod hon) |

| Nodyn: Gallwch ddefnyddio papurau wal arbed sgrin deinamig i osgoi ôl-ddelweddau a achosir gan arddangosiad tudalen sefydlog am amser hir. | |

| Math | CTP (panel cyffwrdd capacitive) |

| Strwythur | Strwythur G+G gyda gorchudd wyneb o wydr tymherus |

| Modd Cyffwrdd | Cefnogi pwynt cyffwrdd a llusgo |

| Caledwch Arwyneb | 6H |

| Trosglwyddiad Ysgafn | Dros 90% |

| Bywyd | Dros 1,000,000 o weithiau'n cyffwrdd |

| Math | RTP (panel cyffwrdd gwrthiannol) |

| Strwythur | Y ffilm HWN + gwydr HWN |

| Modd Cyffwrdd | Cefnogi pwynt cyffwrdd a llusgo |

| Caledwch Arwyneb | 3H |

| Trosglwyddiad Ysgafn | Dros 80% |

| Bywyd | Dros 1,000,000 o weithiau'n cyffwrdd |

| Modd |

UART2: ON=TTL/CMOS; OFF=RS232(RS232 diofyn) UART4: ON=TTL/CMOS; OFF=RS232 (Dim ond ar gael ar ôl ffurfweddiad OS) | |||||

| Lefel Foltedd | Cyflwr Prawf | Minnau | Math | Max | Uned | |

| Allbwn 1, Iout = -4mA | 2.7 | 3.2 | - | YN | ||

| Allbwn 0, Iout = 4mA | - | 0.1 | 0.4 | YN | ||

| Mewnbwn 1 | 2.4 | 3.3 | 5.5 | YN | ||

| Mewnbwn 0 | 0 | - | 1.0 | YN | ||

| Cyfradd Baud | 3150 ~ 3225600bps, gwerth nodweddiadol o 115200bps | |||||

| Fformat Data |

UART2: N81 UART4: N81/E81/O81/N82 , 4 modd (cyfluniad OS) | |||||

| Cebl Rhyngwyneb | 8Pin_2.0mm | |||||

| Pŵer â Gradd | ||||||

| Foltedd Gweithredu | 8 ~ 36V, gwerth nodweddiadol o 12V | |||||

| Cyfredol Gweithredol | 440mA | VCC=12V, golau ôl mwyaf | ||||

| 160mA | VCC=12V, golau cefn i ffwrdd | |||||

| Cyflenwad pŵer a argymhellir: 12V 1A DC | ||||||

| Tymheredd Gweithredu | -20 ℃ ~ 70 ℃ (12V @ 60% RH) | |||||

| Tymheredd Storio | -30 ℃ ~ 80 ℃ | |||||

| Gorchudd Cydymffurfio | Oes | |||||

| Lleithder Gweithredu | 10% ~ 90% RH, gwerth nodweddiadol o 60% RH | |||||