——Агульны доступ ад DWIN Froum

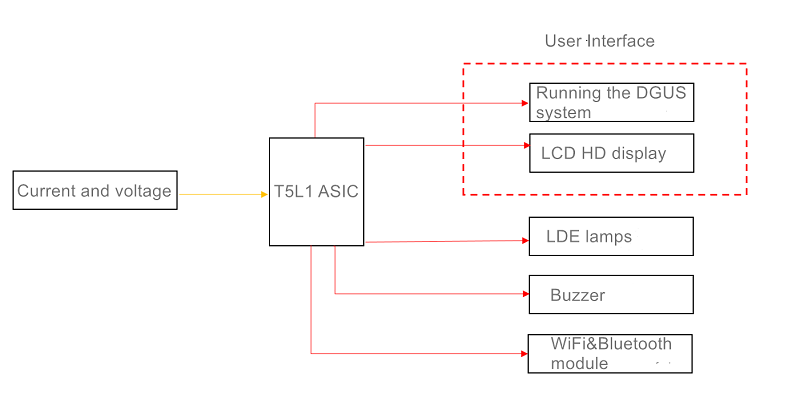

Выкарыстоўваючы чып DWIN T5L1 у якасці ядра кіравання ўсёй машынай, ён прымае і апрацоўвае інфармацыю аб дотыку, зборы АЦП, ШІМ-кіраванні і кіруе 3,5-цалевым ВК-экранам для адлюстравання бягучага стану ў рэжыме рэальнага часу. Падтрымка дыстанцыйнага сэнсарнага рэгулявання яркасці святлодыёднай крыніцы святла праз модуль WiFi і падтрымка галасавой сігналізацыі.

Асаблівасці праграмы:

1. Прыняць чып T5L для працы на высокай частаце, аналагавая выбарка AD стабільная, а памылка невялікая;

2. Падтрымка TYPE C, непасрэдна падключаная да ПК для адладкі і запісу праграм;

3. Падтрымка высакахуткаснага асноўнага інтэрфейсу АС, 16-бітны паралельны порт; ШІМ-порт ядра карыстальніцкага інтэрфейсу, вывад порта AD, недарагі дызайн прыкладанняў, няма неабходнасці дадаваць дадатковыя MCU;

4. Падтрымка WiFi, Bluetooth дыстанцыйнага кіравання;

5. Падтрымка 5~12В пастаяннага току шырокага напружання і шырокага ўваходнага дыяпазону

1.1 Схема-схема

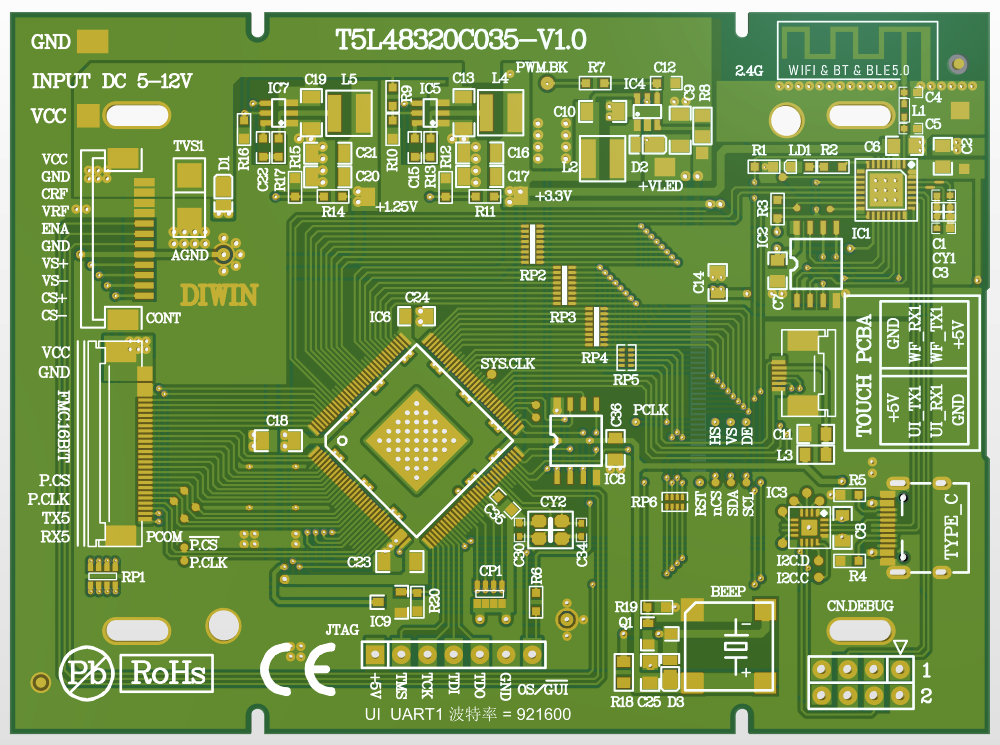

Плата друкаванай платы 1.2

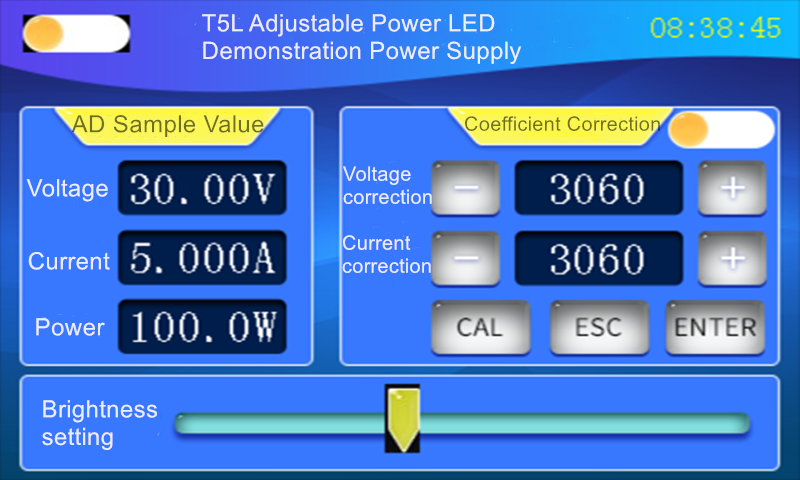

1.3 Інтэрфейс карыстальніка

Увядзенне ганьбы:

(1)Праектаванне апаратнай схемы

1.4 Электрычная схема T5L48320C035

1. Лагічны блок харчавання MCU 3.3V: C18, C26, C27, C28, C29, C31, C32, C33;

2. Ядро сілкавання MCU 1.25V: C23, C24;

3. Аналагавы блок сілкавання MCU 3,3 В: C35 - аналагавы блок сілкавання для MCU. Пры наборы зазямленне ядра 1,25 В і лагічнае зазямленне можна аб'яднаць, але аналагавае зазямленне павінна быць раз'яднана. Аналагавае зазямленне і лічбавае зазямленне павінны быць сабраны на адмоўным полюсе выхаднога кандэнсатара LDO вялікага памеру, а аналагавы станоўчы полюс таксама павінен быць сабраны на станоўчым полюсе вялікага кандэнсатара LDO, каб шум выбаркі AD быў зведзены да мінімуму.

4. Схема збору аналагавага сігналу AD: CP1 - кандэнсатар аналагавага ўваходнага фільтра AD. Каб паменшыць памылку выбаркі, аналагавая і лічбавая зазямленне MCU падзеленыя незалежна. Адмоўны полюс CP1 павінен быць падлучаны да аналагавай зямлі MCU з мінімальным імпедансам, а два паралельныя кандэнсатары кварцавага асцылятара падлучаны да аналагавай зямлі MCU.

5. Схема зумера: C25 - гэта кандэнсатар крыніцы харчавання для зумера. Зумер - гэта індуктыўная прылада, і падчас працы будзе назірацца пік току. Каб паменшыць пік, неабходна паменшыць ток узбуджэння MOS зумера, каб прымусіць трубку MOS працаваць у лінейнай вобласці, і распрацаваць схему, каб яна працавала ў рэжыме пераключэння. Звярніце ўвагу, што R18 павінен быць падключаны паралельна на абодвух канцах зумера, каб наладзіць якасць гуку зумера і зрабіць гук зумера выразным і прыемным.

6. Схема WiFi: выбарка чыпа WiFi ESP32-C з WiFi+Bluetooth+BLE. На праводцы зазямленне радыёчастотнага сілкавання і зазямленне сігналу падзеленыя.

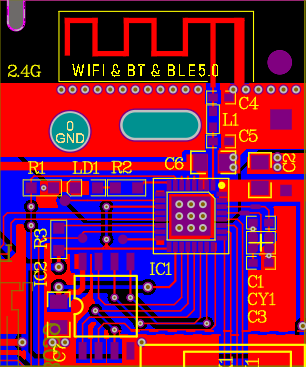

1.5 Дызайн схемы WiFi

На малюнку вышэй верхняя частка меднага пакрыцця - гэта контур зазямлення. Адбівальны контур зазямлення антэны WiFi павінен мець вялікую плошчу да зазямлення, а кропкай збору зазямлення з'яўляецца адмоўны полюс C6. Паміж зазямленнем сілкавання і антэнай WiFi неабходна забяспечыць адбіты ток, таму пад антэнай WiFi павінна быць меднае пакрыццё. Даўжыня меднага пакрыцця перавышае даўжыню выцягвання антэны WiFi, і пашырэнне павялічыць адчувальнасць WiFi; пункт на адмоўным полюсе C2. Вялікая плошча медзі можа экранаваць шум, выкліканы выпраменьваннем антэны WiFi. 2 медныя зазямленні падзелены на ніжнім пласце і збіраюцца да сярэдняй пляцоўкі ESP32-C праз адтуліны. Зазямленне радыёчастотнага сілкавання мае патрэбу ў меншым супраціве, чым контур зазямлення сігналу, таму ёсць 6 пераходных адтулін ад зазямлення сілкавання да пляцоўкі мікрасхемы, каб забяспечыць дастаткова нізкі імпеданс. Праз контур зазямлення кварцавага генератара не можа праходзіць радыёчастотная магутнасць, у адваротным выпадку кварцовы генератар будзе генераваць дрыгаценне частоты, і зрушэнне частоты WiFi не зможа адпраўляць і атрымліваць даныя.

7. Схема харчавання святлодыёднай падсветкі: выбарка чыпа драйвера SOT23-6LED. Блок сілкавання пастаяннага і пастаяннага току для святлодыёда незалежна адзін ад аднаго ўтварае шлейф, а зазямленне пастаяннага і пастаяннага току злучана з зазямленнем 3,3 В LOD. Паколькі ядро порта PWM2 было спецыялізаванае, яно выдае сігнал 600K ШІМ, а RC дададзены для выкарыстання выхаду ШІМ у якасці кіравання ВКЛ/ВЫКЛ.

8. Дыяпазон уваходнага напружання: распрацаваны два паніжальныя DC/DC. Звярніце ўвагу, што рэзістары R13 і R17 у ланцугу пастаяннага і пастаяннага току нельга прапусціць. Дзве мікрасхемы DC/DC падтрымліваюць уваходнае напружанне да 18 В, што зручна для знешняга сілкавання.

9. Порт адладкі USB TYPE C: TYPE C можна падключаць і адключаць наперад і назад. Устаўка наперад звязваецца з чыпам WIFI ESP32-C для праграмавання чыпа WIFI; зваротная ўстаўка ўзаемадзейнічае з XR21V1410IL16 для праграмавання T5L. TYPE C падтрымлівае крыніцу харчавання 5 В.

10. Сувязь праз паралельны порт: ядро АС T5L мае мноства свабодных партоў уводу-вываду, і можна распрацаваць сувязь праз 16-бітны паралельны порт. У спалучэнні з пратаколам паралельнага порта ST ARM FMC ён падтрымлівае сінхроннае чытанне і запіс.

11. Дызайн высакахуткаснага інтэрфейсу LCM RGB: выхад T5L RGB напрамую падлучаны да LCM RGB, а буфернае супраціўленне дададзена ў сярэдзіне, каб паменшыць перашкоды ад пульсацыі вады LCM. Пры падключэнні паменшыце даўжыню злучэння інтэрфейсу RGB, асабліва сігналу PCLK, і павялічце кантрольныя кропкі інтэрфейсу RGB PCLK, HS, VS, DE; порт SPI экрана падлучаны да партоў P2.4~P2.7 T5L, што зручна для распрацоўкі драйвера экрана. Вывядзіце тэставыя кропкі RST, nCS, SDA, SCI, каб палегчыць распрацоўку асноўнага праграмнага забеспячэння.

(2) Інтэрфейс DGUS

1.6 Кантроль адлюстравання зменных дадзеных

(3) АС

//———————————Фармат чытання і запісу DGUS

typedef struct

{

u16 адрас; //16-бітны зменны адрас карыстацкага інтэрфейсу

u8 datLen; //8-бітная даўжыня даных

u8 *pBuf; //8-бітны паказальнік даных

} UI_packTypeDef; //Пакеты чытання і запісу DGUS

//———————————кантроль адлюстравання зменных дадзеных

typedef struct

{

у16 ВП;

u16 X;

u16 Y;

u16 Колер;

u8 Lib_ID;

u8 Памер шрыфта;

u8 Выраўноўванне;

u8 IntNum;

u8 DecNum;

тып u8;

u8 LenUint;

u8 StringUinit[11];

} Number_spTypeDef; // структура апісання зменнай дадзеных

typedef struct

{

Number_spTypeDef sp; //вызначыць паказальнік апісання SP

UI_packTypeDef spPack; //вызначыць зменную SP DGUS для чытання і запісу пакета

UI_packTypeDef vpPack; //вызначэнне пакета чытання і запісу зменнай vp DGUS

} Number_HandleTypeDef; // структура зменнай даных

З папярэднім вызначэннем пераменнай дадзеных. Затым вызначыце зменную для дысплея выбаркі напружання:

Number_HandleTypeDef Hsample;

u16 выбарка напружання;

Спачатку выканайце функцыю ініцыялізацыі

NumberSP_Init(&Hsample,voltage_sample,0×8000); //0×8000 тут паказальнік апісання

//——Зменная даных, якая паказвае ініцыялізацыю структуры паказальніка SP——

void NumberSP_Init(Number_HandleTypeDef *number,u8 *value, u16 numberAddr)

{

number->spPack.addr = numberAddr;

нумар->spPack.datLen = sizeof(нумар->sp);

нумар->spPack.pBuf = (u8 *)&нумар->sp;

Read_Dgus(&number->spPack);

нумар->vpPack.addr = нумар->sp.VP;

switch(number->sp.Type) //Даўжыня даных зменнай vp выбіраецца аўтаматычна ў адпаведнасці з тыпам зменнай даных, распрацаваным у інтэрфейсе DGUS.

{

выпадак 0:

выпадак 5:

нумар->vpPack.datLen = 2;

разбіваць;

выпадак 1:

выпадак 2:

выпадак 3:

выпадак 6:

нумар->vpPack.datLen = 4;

выпадак 4:

нумар->vpPack.datLen = 8;

разбіваць;

}

нумар->vpPack.pBuf = значэнне;

}

Пасля ініцыялізацыі Hsample.sp з'яўляецца паказальнікам апісання зменнай выбаркі напружання; Hsample.spPack - гэта ўказальнік сувязі паміж ядром АС і зменнай выбаркі напружання карыстацкага інтэрфейсу праз функцыю інтэрфейсу DGUS; Hsample.vpPack - гэта атрыбут змены зменнай выбаркі напружання, такія як колеры шрыфта і г.д., якія таксама перадаюцца ў ядро карыстацкага інтэрфейсу праз функцыю інтэрфейсу DGUS. Hsample.vpPack.addr - гэта адрас зменнай даных выбаркі напружання, які быў аўтаматычна атрыманы з функцыі ініцыялізацыі. Калі вы змяняеце адрас зменнай або тып зменных даных у інтэрфейсе DGUS, няма неабходнасці сінхронна абнаўляць адрас зменнай у ядры АС. Пасля таго як ядро АС вылічыць зменную voltage_sample, яму трэба толькі выканаць функцыю Write_Dgus(&Hsample.vpPack), каб абнавіць яе. Для перадачы DGUS няма неабходнасці ўпакоўваць Voltage_sample.

Час публікацыі: 15 чэрвеня 2022 г